QuartusII调用 PLL_IP核方法(Mega Wizard)

【基本信息】

要求:调用PLL—IP核,50Mhz晶振输入,输出四路时钟不同信号:100Mhz,25Mhz,50Mhz(90°相位),50Mhz(20%占空比)。

芯片型号:cyclone Ⅳ EP4CE10F17C8

平台工具:Quartus II 15.0 (64-bit)、Modelsim SE-64 10.4

【PLL_IP核简介】

IP核:ASIC或FPGA中预先设计好具有某种功能的电路模块,参数可修改,目的在于提高开发效率。

QuartusII软件下IP核调用方式:Mega Wizard插件管理器(常用)、SOPC构造器、DSP构造器、Qsys设计系统例化。

PLL(Phase Lockded Loop,锁相环)常用IP核之一,可对输入时钟信号进行任意分频、倍频、相位、占空比调整。Altera 模拟锁相环,优点:信号稳定度高,相位连续可调,延时连续可调;缺点:受温度、电磁辐射影响,可能失锁。

【PLL_IP核配置】

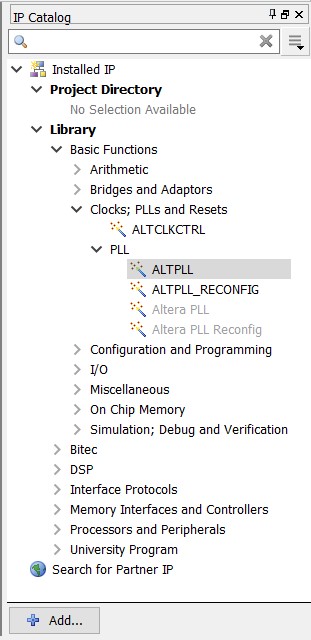

进入QuartusII,直接打开Mega Wizard插件管理器或者打开工具菜单栏下IP—catalog,PLL-ALTPLL。

1、配置第一步进行参数/模式设置。

注意模式区别:

源同步:使用于高速数据接口,若数据和时钟同时到达输入管脚,那么在 I/O 单元输入寄存器的数据与时钟端口,数据与时钟之间的相位关系保持不变。

无补偿:PLL 不对任何时钟网络进行补偿 (允许延迟),相对 PLL 时钟输入,PLL 内部以及外部时钟输出均有相位偏移。

标准:内部时钟是与输入时钟管脚相位对齐 ,若连接外部时钟输出管脚,则外部时钟输出管脚会产生相对于时钟输入管脚的相位延迟 ,标准模式的时钟最好作用在寄存器上。

零延迟缓冲:外部时钟输出管脚与时钟输入管脚是相位对齐的,没有延迟,作用输出不建议作用寄存器。

2、配置信号输入和锁定输出设置:

3、Bandwidth/CSS和时钟切换这些高级属性配置跳过即可。

4、PLL Reconfiguration动态/动态相位重配置跳过。

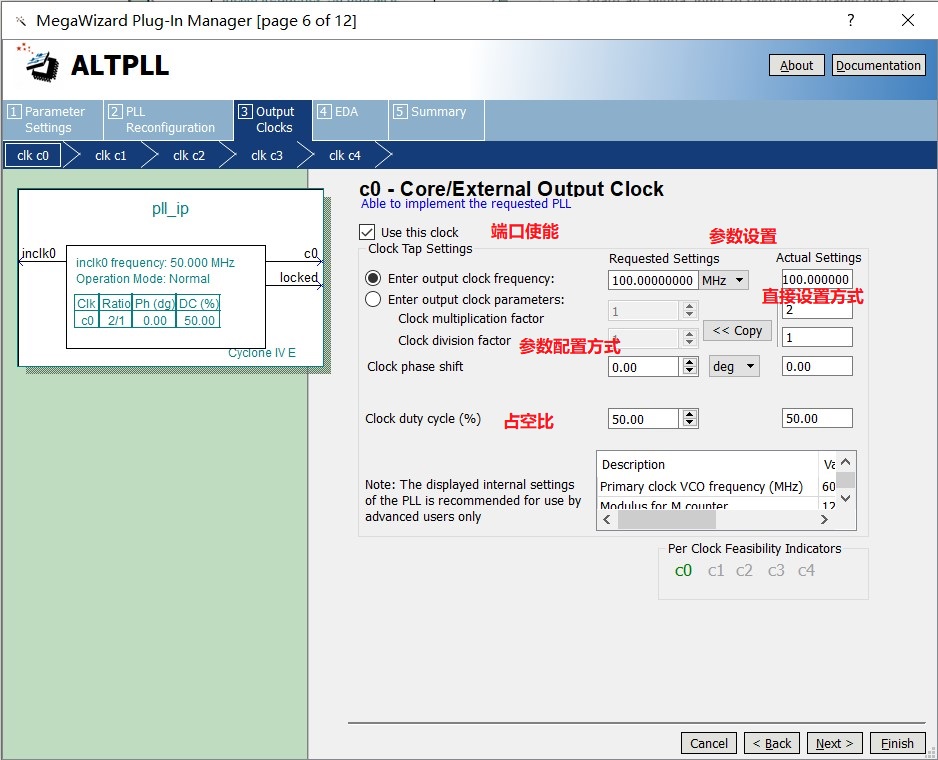

5、输出时钟信号配置(重点),共可输出五路信号,输出勾选使能,按需配置频率、占空比、相位。

配置完成,继续下一步,如果采用modelsim外部仿真软件的话,可以看到所需的仿真库。

最后确认页面,左边图可看到PLL_IP产生了四路时钟信号和一路锁定信号,时钟信号参数类型很清楚。最后需要勾选inst.v实例化文件,方便后面调用IP核。

【PLL_IP核调用】

1、IP核调用

pll_ip_inst.v文件就是PLL_IP核实例模块,这里简单写个顶层文件调用即可,可以通过引脚配置上机测试下输出。

`module ip_pll(

input sys_clk,

output clk_100Mhz ,

output clk_25Mhz ,

output clk_50Mhz_90deg ,

output clk_50Mhz_20DC ,

output locked_sig

);

pll_ip pll_ip_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_100Mhz ),

.c1 ( clk_25Mhz ),

.c2 ( clk_50Mhz_90deg ),

.c3 ( clk_50Mhz_20DC ),

.locked ( locked_sig )

);

endmodule

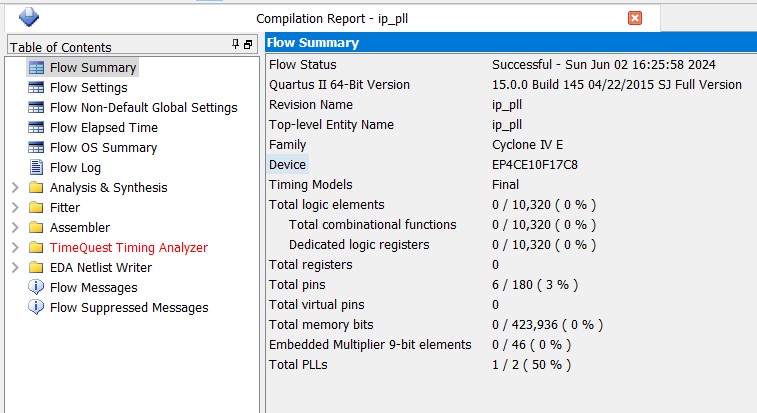

对工程文件全编译,可以看到(下图),芯片资源的使用情况,EP4CE10F17C8有两个PLL,其他逻辑电路没有使用。

2、使用技巧

PLL_IP编辑好,后期修改有两种方式:第一种是在Quartus主页左上方Project Navigator-IP Components双击打开目标IP核,还有一种就是在Mega Wizard插件管理器,选择编辑现有IP核。

如果不小心把IP核删除了,只需重新添加目标IP核文件,后缀.qip(主文件)添加应用。需要复制现有IP核,只需打包IP核文件,后缀包括.v;inst.v;.qip;.ppf;greybox_tmp五个文件,然后添加应用到工程文件。

【PLL_IP核仿真】

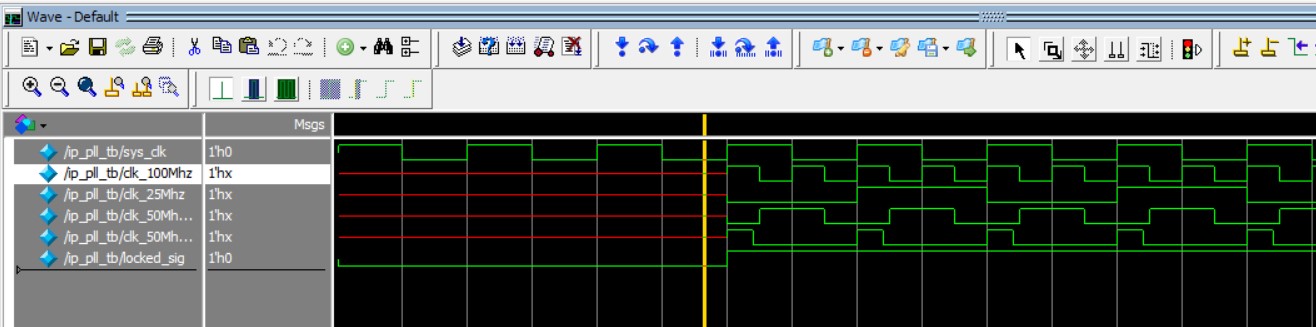

在仿真结果中,首先可以观察到锁相环的锁定过程。在这个过程中,锁相环的输出信号(locked信号)会保持低电平状态,表示锁相环尚未锁定,各时钟信号输出会处于不定态,它们的值会随机变化或保持不变。稳定后,很明显看到频率、相位、占空比的调整情况。

Ps:如需要工程重要的文件,在个人博客首页Gitee仓库内可以得到。