飞腾E2000板载以太网适配

飞腾E2000板载以太网适配

飞腾E2000嵌入式板卡的MAC芯片对应linux通用macb驱动,外接YT8521 PHY芯片。飞腾在5.10内核上进行过适配,现将其移植到麒麟5.4内核。

本文参考资料:

飞腾5.10内核源码

飞腾E2000以太网驱动注册和使用简介

飞腾腾珑E2000软件编程手册V0.6.pdf

YT8521S初始化配置相关ver2.1.pdf

YT8521SH-CA_YT8521SC-CA_Datasheet_v1.02.pdf

1. 设备树移植

phy-mode为MAC芯片与PHY芯片物理层的连接方式,这涉及到真实的物理连接方式,本文所用的硬件采用rgmii模式。

注:rgmii模式下,tx clk由mac提供,rx clK由phy提供。

macb0: ethernet@3200c000 {

compatible = "cdns,phytium-gem-1.0";

reg = <0x0 0x3200c000 0x0 0x2000>;

interrupts = <GIC_SPI 55 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 56 IRQ_TYPE_LEVEL_HIGH>,

...

<GIC_SPI 30 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 31 IRQ_TYPE_LEVEL_HIGH>;

clock-names = "pclk", "hclk", "tx_clk", "tsu_clk";

clocks = <&sysclk_250mhz>, <&sysclk_48mhz>, <&sysclk_48mhz>, <&sysclk_250mhz>;

magic-packet;

status = "okay";

phy-mode = "rgmii";

use-mii;

};2. MACB驱动移植

飞腾5.10 macb驱动无法直接替换麒麟5.4 macb驱动,因此需要进行手动移植。

根据设备树知道硬件通过cdns,phytium-gem-1.0进行匹配,因此需要在macb_dt_ids中新增cdns,phytium-gem-1.0条目,并将phytium_gem1p0_config移植到麒麟5.4内核中。

drivers/net/ethernet/cadence/macb_main.c:

static const struct macb_config phytium_gem1p0_config = {

.caps = MACB_CAPS_GIGABIT_MODE_AVAILABLE |

MACB_CAPS_JUMBO |

MACB_CAPS_GEM_HAS_PTP |

MACB_CAPS_BD_RD_PREFETCH |

MACB_CAPS_SEL_CLK,

.dma_burst_length = 16,

.clk_init = phytium_clk_init,

.init = phytium_init,

.jumbo_max_len = 16360,

.sel_clk_hw = phytium_gem1p0_sel_clk,

};

static const struct of_device_id macb_dt_ids[] = {

...

{ .compatible = "cdns,phytium-gem-1.0", .data = &phytium_gem1p0_config },

...

}由于麒麟5.4 macb驱动与飞腾5.10 macb驱动有所差别,仅移植以上部分还不够。

根据phytium_gem1p0_config的定义,其中包含了.sel_clk_hw = phytium_gem1p0_sel_clk,但在麒麟5.4 macb驱动中并未定义和使用phytium_gem1p0_sel_clk函数。

查看飞腾5.10内核phytium_gem1p0_sel_clk函数实现及调用,发现当caps & MACB_CAPS_SEL_CLK成立时该函数才会被调用,并且在麒麟5.4内核中存在功能等价的替代函数phytium_gem_sel_clk,该替代函数只有caps & MACB_CAPS_SEL_CLK_HW成立时才被调用。

飞腾5.10

drivers/net/ethernet/cadence/macb_main.c:

static void macb_mac_link_up(struct phylink_config *config,

struct phy_device *phy,

unsigned int mode, phy_interface_t interface,

int speed, int duplex,

bool tx_pause, bool rx_pause)

{

... ...

if (bp->caps & MACB_CAPS_SEL_CLK)

bp->sel_clk_hw(bp, speed);

... ...

}麒麟5.4

static void macb_handle_link_change(struct net_device *dev)

{

... ...

if (bp->caps & MACB_CAPS_SEL_CLK_HW)

phytium_gem_sel_clk(bp);

... ...

}综上,最终驱动的移植方案是使用phytium_gem_sel_clk + MACB_CAPS_SEL_CLK_HW替代phytium_gem1p0_sel_clk + MACB_CAPS_SEL_CLK如下:

drivers/net/ethernet/cadence/macb_main.c:

static const struct macb_config phytium_gem1p0_config = {

.caps = MACB_CAPS_GIGABIT_MODE_AVAILABLE |

MACB_CAPS_JUMBO |

MACB_CAPS_GEM_HAS_PTP |

MACB_CAPS_BD_RD_PREFETCH |

MACB_CAPS_SEL_CLK_HW,

.dma_burst_length = 16,

.clk_init = phytium_clk_init,

.init = phytium_init,

.jumbo_max_len = 16360,

//.sel_clk_hw = phytium_gem1p0_sel_clk,

};

static const struct of_device_id macb_dt_ids[] = {

...

{ .compatible = "cdns,phytium-gem-1.0", .data = &phytium_gem1p0_config },

...

}3. 网络连通性调试

macb驱动移植成功之后,网络顺利UP,但无法ping通.

netstat -i可以看到存在RX-OK、TX-OK计数,并且计数正常累加。这里基本可以说明MAC层收发是正常的。

利用tcpdump抓包发现,虽然TX-OK正常累加,但对端陪测机无法抓到被测机所发的任何数据包,被测机能抓到陪测机发的数据包,基本确定网络只能收不能发。

3-1. MACB驱动环回测试

飞腾腾珑E2000软件编程手册V0.6.pdf中,以太网基地址如下:

在0x00 network_control寄存器中bit1为本地环回寄存器,将该bit位置1。

devmem2 $((0x32010000+0x00)) h #读0x00寄存器的值

0x1c

devmem2 $((0x32010000+0x00)) h 0x1e #写0x00寄存器,将bit1置1.进行ping环回抓包测试,测试通过,排除MAC层异常。

3-2. YT8521 PHY工作模式及电压确认

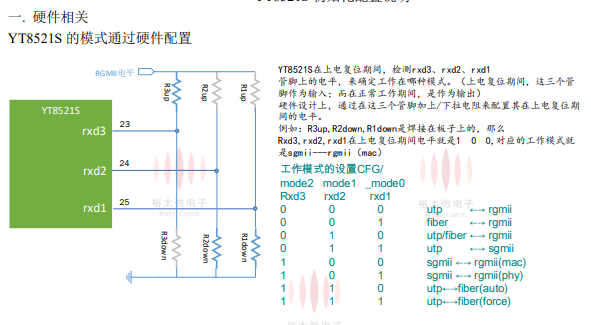

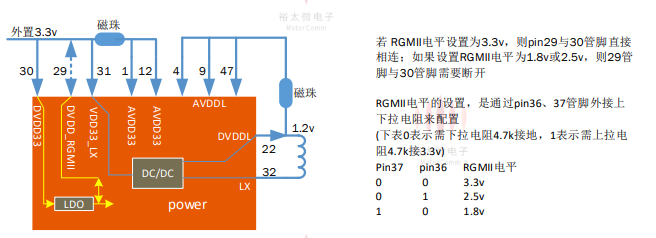

phy的工作模式和电压与硬件强相关,可以通过读取0xa001扩展配置寄存器,确认phy工作模式与实际物理连接是否一致。

root@kylin:/opt/phytool# ./phytool write eth1/0x0/0x1e 0xa001 && ./phytool eth1/0x0/0x1f

ieee-phy: reg:0x1f val:0x81400xa001寄存器的值为0x8140,因此phy的工作模式配置为UTP_TO_RGMII,电压为3.3v。

3-3. YT8521 PHY环回测试

在YT8521SH-CA_YT8521SC-CA_Datasheet_v1.02.pdf中PHY环回寄存器中,0x00基本控制寄存器bit14位是环回使能位。

需要说明的是在进行环回测试时,需要将PHY Autonet_En关闭,否则网口无法UP。

./phytool write eth1/0x0/0x00 0x4140

./phytool eth1/0x0/0x00这里phy 环回测试未通过,可以确定PHY未将数据发送出去,问题在PHY层发送方向。

3-4. YT8521 PHY tx delay调整

RGMII模式下,MAC负责提供TX时钟,PHY提供RX时钟。通过macb驱动确认1000M带宽下tx时钟频率为125MHz,确认时钟频率正常。

drivers/net/ethernet/cadence/macb_main.c:

static void macb_set_tx_clk(struct clk *clk, int speed, struct net_device *dev)

{

... ...

switch (speed) {

... ...

case SPEED_1000:

rate = 125000000;

break;

default:

return;

}

rate_rounded = clk_round_rate(clk, rate);

if (rate_rounded < 0)

return;

/* RGMII allows 50 ppm frequency error. Test and warn if this limit

* is not satisfied.

*/

ferr = abs(rate_rounded - rate);

ferr = DIV_ROUND_UP(ferr, rate / 100000);

if (ferr > 5)

netdev_warn(dev, "unable to generate target frequency: %ld Hz\n",

rate);

if (clk_set_rate(clk, rate_rounded))

netdev_err(dev, "adjusting tx_clk failed.\n");

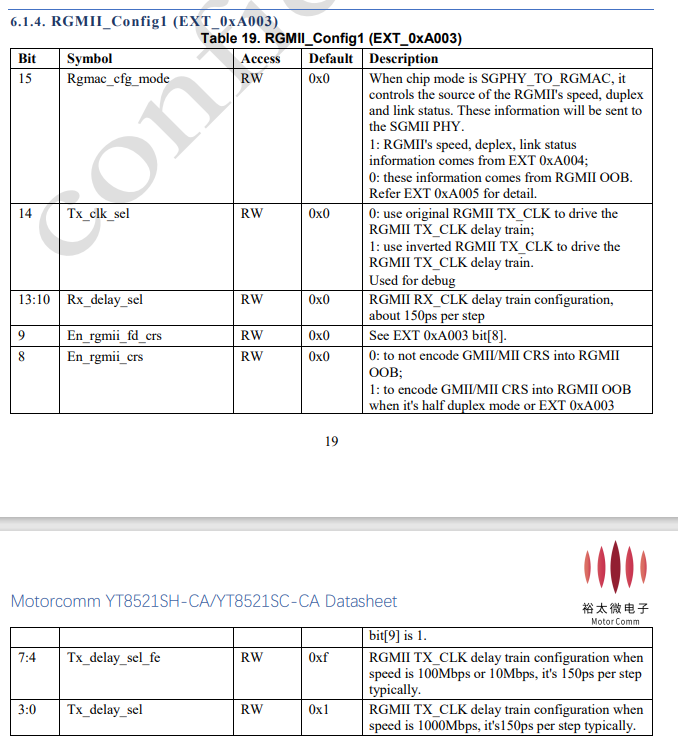

}查看tx clk delay,读取0xa003寄存器,千兆带宽tx clk delay时延由bit3:0提供。

root@kylin:/opt/phytool# ./phytool write eth1/0x0/0x1e 0xa003 && ./phytool eth1/0x0/0x1f

ieee-phy: reg:0x1f val:0x00f10xa003 bit3:0 默认为1,时延150ps,根据YT8521S初始化配置相关ver2.1.pdf资料,业内默认rgmii模式下tx clk delay默认为750ps。

修改0xa003寄存器为750ps,千兆依然不通,从150ps增加到450ps时,可以ping通,但存在丢包的情况,继续增加时延到1200ps(8*150ps)时,可以ping通,ping未看到丢包,千兆带宽测试正常。

./phytool write eth1/0x0/0x1e 0xa003

./phytool write eth1/0x0/0x1f 0x00f8 附:

时钟精度(Frequency Tolerance):时钟精度一般是25℃下测量额时钟相对于标准频率的偏差,单位ppm(百万分之一),例如测得精度为±15ppm,时钟频率为25MHz,周期为1/25MHz=40ns,精度偏差为40ns×(±15/1000000)=0.6ps

时钟温漂(Frequency versus Temperature Characteristics):由于晶振材料和工艺限制,致使时钟在不同的温度下精度会有较大偏差,单位也为ppm。例如温漂为±100ppm,时钟频率为25MHz,周期为1/25MHz=40ns,精度偏差为40ns×(±100/1000000)=4ps

时钟抖动(Jitter):晶振源固有的噪声和干扰通常会带来时钟信号的周期性偏差。单位一般为ps

本文来自博客园,作者:StepForwards,转载请注明原文链接:https://www.cnblogs.com/forwards/p/17864696.html

热门相关:虚张声势 惊世第一妃 百炼成仙 全系灵师:魔帝嗜宠兽神妃 宝贝迷人,总裁圈住爱